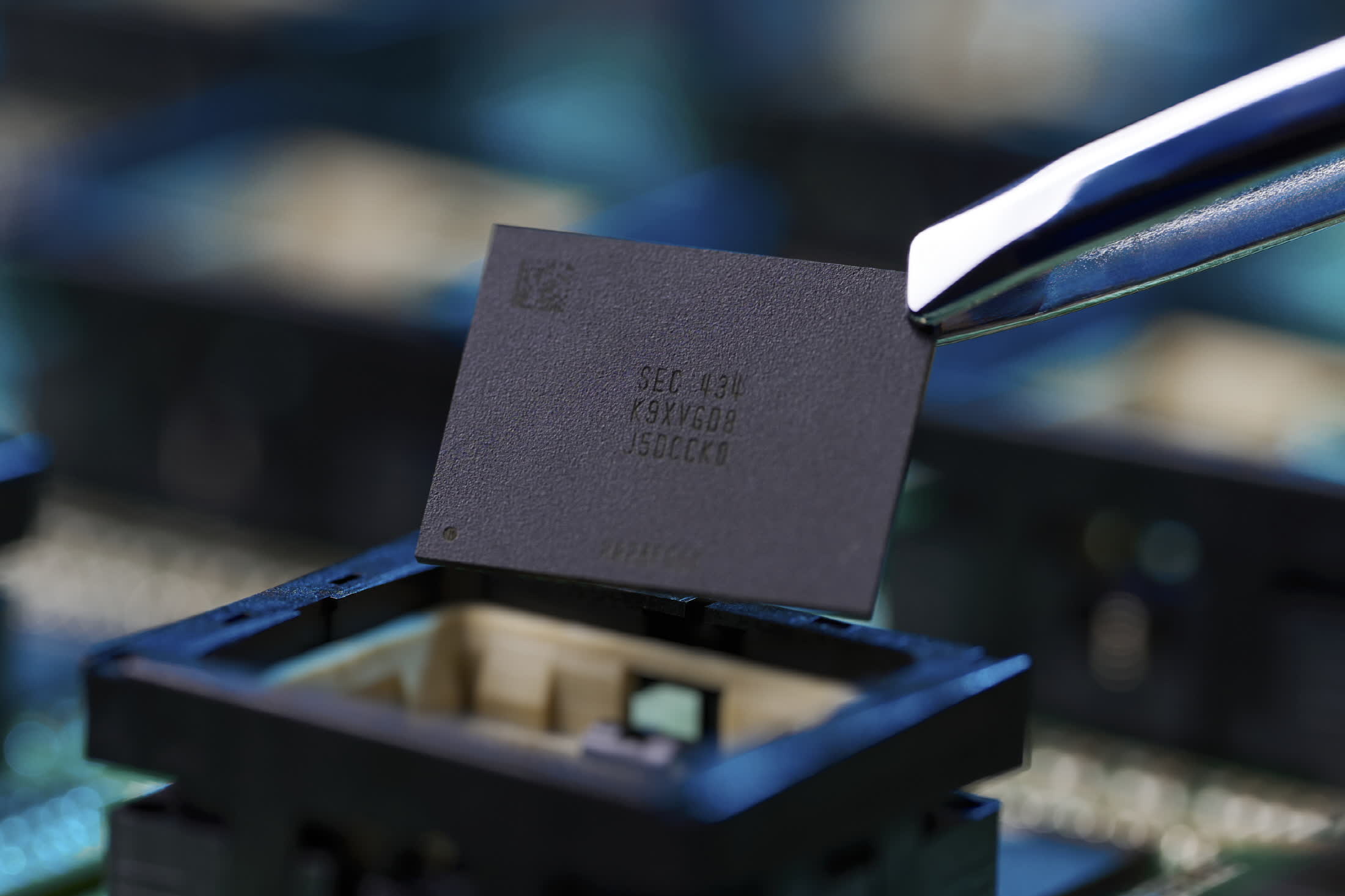

Why it issues: Samsung’s V-NAND know-how has superior considerably, rising from 24 layers to almost 300 layers in simply over a decade. Though the corporate has confronted vital challenges in extra scaling, it stays assured that it might match not less than 400 layers of flash reminiscence cells into NAND chips. If all goes as deliberate, mass manufacturing may start by the tip of subsequent yr.

Samsung’s Ninth-generation 280-layer V-NAND flash reminiscence has solely lately entered mass manufacturing, with the primary business merchandise anticipated to hit retailer cabinets subsequent yr. Nonetheless, in line with the Korea Financial Day by day, the corporate is already setting formidable targets for its Tenth-generation 400-layer V-NAND know-how.

Competitors within the house has intensified in recent times, pushed largely by the rising calls for of AI functions, together with a rising shopper urge for food for bigger and extra inexpensive flash storage.

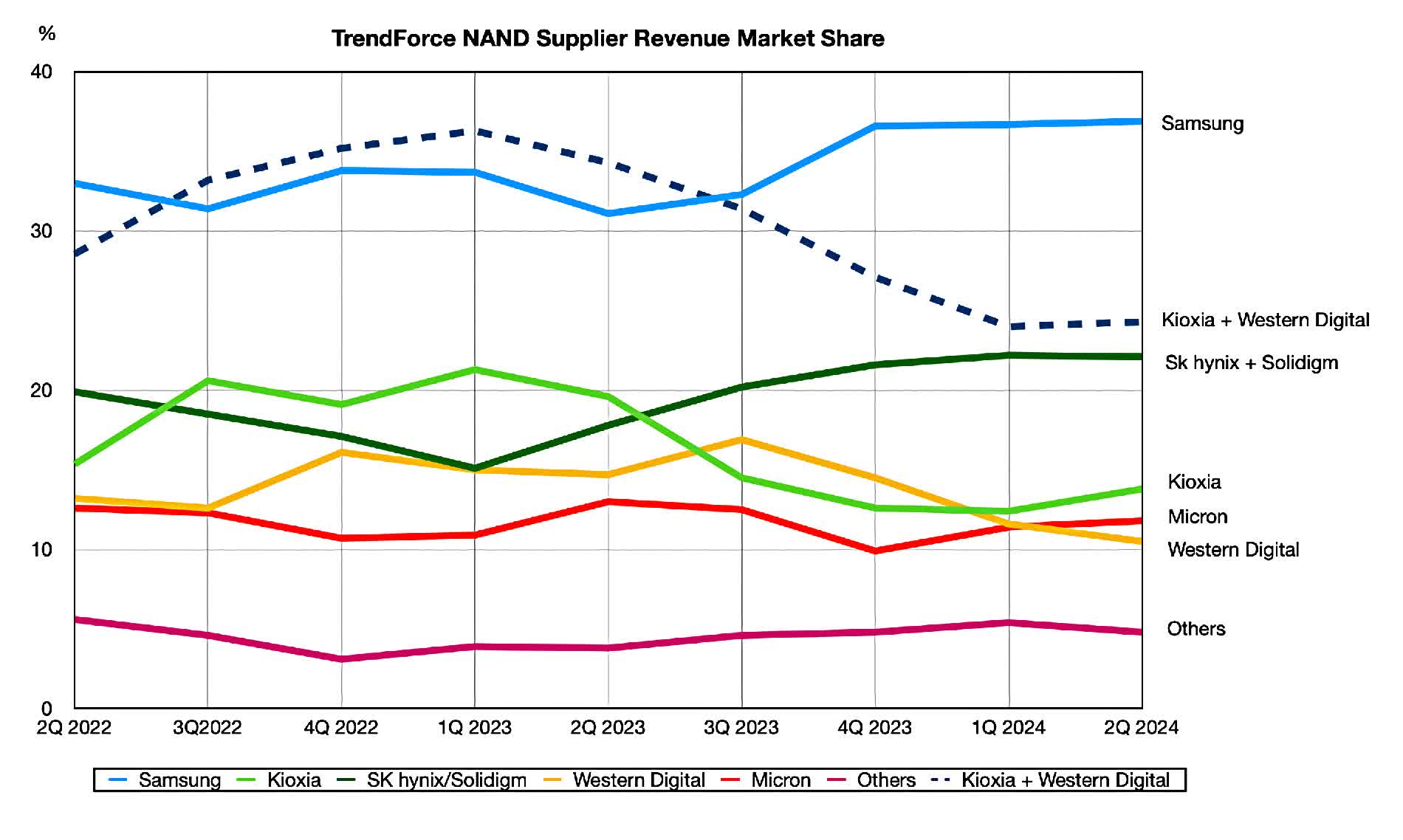

Samsung at the moment holds a number one 37 % market share, however sustaining that place is changing into more and more difficult as opponents like Micron, YMTC, SK Hynix, and Kioxia speed up their growth of higher-density 3D NAND.

SK Hynix plans to start manufacturing 400-layer NAND by the tip of 2025, with full-scale manufacturing anticipated within the first half of 2026. This has prompted Samsung to focus on the identical timeline, as its smaller Korean rival has gained vital market share over the previous two years.

Stacking 400 or extra layers of NAND isn’t any straightforward feat, as scaling past 300 layers has already posed challenges to the reliability of early prototypes. To deal with this, Samsung plans to make use of a Tri-Stage Cell (TLC) structure alongside a brand new know-how referred to as Bonding Vertical NAND (BV NAND), which separates reminiscence cells and peripheral circuitry onto completely different wafers, that are then bonded collectively in a vertical construction.

This method may even assist Samsung obtain larger manufacturing yields in comparison with these of the Cell over Periphery (CoP) NAND design. The corporate claims it might attain densities of 28Gb/mm², or 1Tb (128GB) per die, which is barely barely decrease than the density achieved with a Ninth-generation Quad-Stage Cell (QLC) structure. Moreover, the 5.6Gb/s information price per pin gives a big efficiency enhance over the three.2Gb/s most achievable with the earlier design.

In principle, future Samsung SSDs may attain capacities of as much as 16TB, with speeds approaching the bounds of a PCIe 5.0 x4 interface in sequential reads and writes.

Samsung will current this promising new V-NAND structure in additional element on the upcoming Worldwide Stable-State Circuits Convention in February 2025.